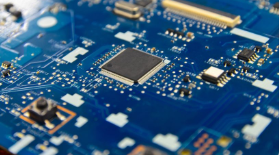

集成電路(IC)是現(xiàn)代電子設(shè)備的核心,其產(chǎn)業(yè)鏈主要包括設(shè)計、制造、封裝和測試等環(huán)節(jié)。其中,芯片封裝技術(shù)作為連接芯片內(nèi)部微觀世界與外部宏觀應(yīng)用的關(guān)鍵橋梁,扮演著至關(guān)重要的角色;而芯片設(shè)計及服務(wù)則是整個產(chǎn)業(yè)的源頭與價值高地,兩者共同構(gòu)成了IC產(chǎn)業(yè)發(fā)展的核心驅(qū)動力。

一、集成電路芯片封裝技術(shù)概述

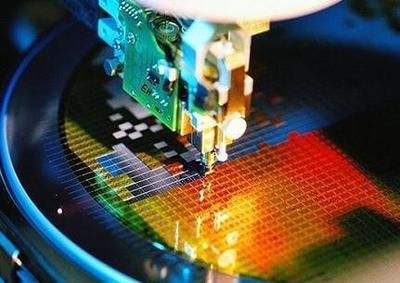

芯片封裝,是指將經(jīng)過制造和測試的晶圓進行切割、分離,并將單個芯片(Die)通過特定工藝安置在封裝基板或框架上,通過引線鍵合或倒裝焊等方式實現(xiàn)電氣連接,并最終用塑料、陶瓷或金屬等材料密封保護,形成獨立、堅固且便于安裝和使用的器件的過程。其主要功能包括:

- 物理保護:保護脆弱且微小的芯片免受機械損傷、環(huán)境污染(如濕氣、灰塵、化學腐蝕)及外部應(yīng)力影響。

- 電氣連接:為芯片提供與外部電路板(PCB)進行電源、信號和地線連接的通道(如引腳、焊球)。

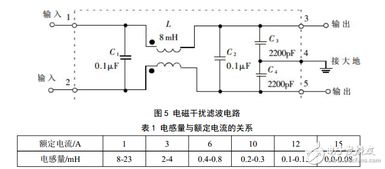

- 散熱管理:將芯片工作產(chǎn)生的熱量有效傳導散發(fā)出去,確保其穩(wěn)定運行。

- 標準規(guī)格化:將不同尺寸、功能的芯片統(tǒng)一成標準尺寸和引腳排列,便于后續(xù)的裝配和測試。

封裝技術(shù)種類繁多,按封裝材料可分為塑料封裝、陶瓷封裝和金屬封裝;按引腳/焊球引出方式可分為通孔插裝型(如DIP)和表面貼裝型(如SOP、QFP、BGA等);按集成度可分為單芯片封裝和多芯片封裝(如MCP、SiP)。隨著電子產(chǎn)品向高性能、小型化、低功耗、多功能發(fā)展,先進封裝技術(shù)已成為關(guān)鍵突破口。

二、集成電路芯片封裝技術(shù)的發(fā)展趨勢

當前,摩爾定律在晶體管微縮方面面臨物理和經(jīng)濟極限,業(yè)界正越來越多地通過“超越摩爾”(More than Moore)路徑,即利用先進封裝技術(shù)來提升系統(tǒng)整體性能,主要發(fā)展趨勢包括:

- 高密度集成:如扇出型晶圓級封裝(Fan-Out WLP)、2.5D/3D封裝(通過硅通孔TSV技術(shù)將多顆芯片在垂直方向堆疊集成),極大地提高了互連密度和系統(tǒng)性能,縮短了信號傳輸路徑。

- 異質(zhì)集成:將不同工藝節(jié)點、不同材質(zhì)(如硅、化合物半導體)、不同功能(邏輯、存儲、射頻、傳感器等)的芯片集成在同一封裝體內(nèi),實現(xiàn)系統(tǒng)級功能,例如系統(tǒng)級封裝(SiP)和芯粒(Chiplet)技術(shù),這是當前最受關(guān)注的領(lǐng)域之一。

- 微型化與薄型化:封裝體尺寸不斷縮小,厚度持續(xù)降低,以滿足可穿戴設(shè)備、手機等便攜式電子產(chǎn)品的需求。

- 高散熱與高可靠性:針對5G、人工智能、高性能計算等產(chǎn)生的高熱流密度,開發(fā)嵌入式微通道液冷、高導熱材料等先進散熱方案,并確保封裝在嚴苛環(huán)境下的長期可靠性。

三、集成電路芯片設(shè)計及服務(wù)概述

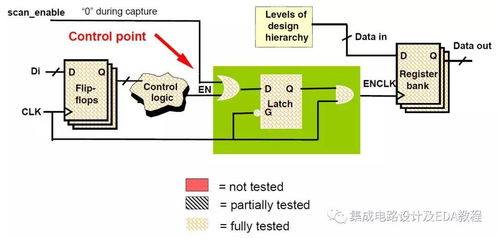

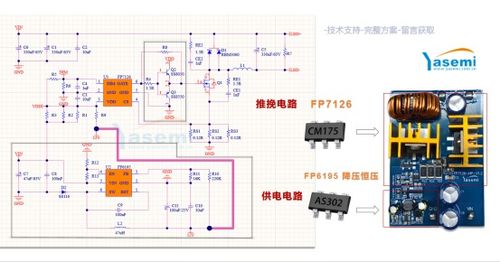

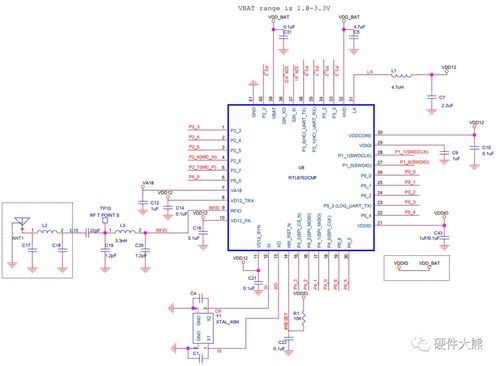

芯片設(shè)計是IC產(chǎn)業(yè)鏈的知識密集型前端環(huán)節(jié),決定了芯片的功能、性能和成本。它是指根據(jù)系統(tǒng)需求,利用電子設(shè)計自動化(EDA)工具,進行電路設(shè)計、邏輯設(shè)計、物理設(shè)計、驗證和簽核等一系列復雜過程,最終生成可供制造用的光刻掩模版(GDSII文件)數(shù)據(jù)。主要設(shè)計流程包括:規(guī)格定義、架構(gòu)設(shè)計、RTL編碼、功能驗證、邏輯綜合、物理設(shè)計(布局布線)、時序/功耗/信號完整性分析、物理驗證等。

隨著工藝進步和系統(tǒng)復雜度激增,設(shè)計成本與風險陡增,催生了多樣化的芯片設(shè)計服務(wù)模式:

- 設(shè)計服務(wù)(Design Service):專業(yè)的集成電路設(shè)計服務(wù)公司,為客戶提供從規(guī)格到GDSII的全流程或部分流程的芯片設(shè)計服務(wù),尤其幫助無晶圓廠(Fabless)公司或系統(tǒng)廠商降低設(shè)計門檻和風險。

- 知識產(chǎn)權(quán)(IP)授權(quán)與服務(wù):提供經(jīng)過驗證的、可復用的IP核(如CPU、GPU、接口、存儲器等),極大加速設(shè)計進程。ARM、Synopsys、Cadence等公司是主要提供者。

- 云上EDA與設(shè)計:利用云計算平臺提供EDA工具和算力資源,支持遠程協(xié)同設(shè)計和彈性算力需求,正成為新興趨勢。

- 芯片定制化服務(wù)(如ASIC/SoC設(shè)計服務(wù)):針對特定應(yīng)用(如AI、汽車、物聯(lián)網(wǎng))提供高度定制化的系統(tǒng)級芯片(SoC)或?qū)S眉呻娐罚ˋSIC)設(shè)計解決方案。

四、芯片設(shè)計服務(wù)的發(fā)展與挑戰(zhàn)

發(fā)展態(tài)勢:

- 與先進工藝深度綁定:設(shè)計服務(wù)必須緊跟5nm、3nm乃至更先進工藝,解決其帶來的物理效應(yīng)、設(shè)計規(guī)則復雜性和高昂的掩模成本等問題。

- Chiplet與先進封裝協(xié)同設(shè)計:設(shè)計服務(wù)不再局限于單顆芯片,而是需要統(tǒng)籌考慮多顆Chiplet的劃分、互連、協(xié)同設(shè)計與先進封裝(如2.5D/3D)的協(xié)同優(yōu)化,即“系統(tǒng)-芯片-封裝”協(xié)同設(shè)計。

- 面向垂直領(lǐng)域深化:針對人工智能、自動駕駛、數(shù)據(jù)中心、物聯(lián)網(wǎng)等特定領(lǐng)域,提供從算法優(yōu)化到芯片實現(xiàn)的全棧式解決方案。

- 開源生態(tài)興起:RISC-V等開源指令集架構(gòu)降低了處理器IP的門檻,促進了開放協(xié)作的設(shè)計生態(tài),設(shè)計服務(wù)需要融入并貢獻于此生態(tài)。

面臨挑戰(zhàn):

- 高昂的人才與工具成本:頂尖設(shè)計工程師稀缺,先進EDA工具授權(quán)費用昂貴。

- 設(shè)計復雜性管理:超大規(guī)模SoC包含數(shù)百億晶體管,確保功能正確、性能達標、功耗可控、一次性流片成功是巨大挑戰(zhàn)。

- 供應(yīng)鏈安全與自主可控:在全球產(chǎn)業(yè)鏈調(diào)整背景下,保障設(shè)計工具、核心IP、制造環(huán)節(jié)的安全與自主可控成為重要議題。

集成電路芯片封裝技術(shù)與設(shè)計服務(wù)是相輔相成的兩大支柱。先進封裝技術(shù)為芯片設(shè)計提供了突破物理極限、實現(xiàn)系統(tǒng)級創(chuàng)新的新維度;而復雜、創(chuàng)新的芯片設(shè)計需求又不斷驅(qū)動著封裝技術(shù)的演進。兩者的深度融合與協(xié)同創(chuàng)新,將是推動集成電路產(chǎn)業(yè)持續(xù)向前,滿足萬物互聯(lián)與智能時代需求的關(guān)鍵所在。